基本上,解码器是一个组合逻辑电路,其将编码输入转换为所提供的两者彼此不同。该名称解码器意味着将编码信息从一种格式转换为另一个格式。因此输入代码通常具有比输出代码字更少的位数。

数字解码器将一组数字信号转换为对应的十进制代码。解码器在使用编码器之前也是最常用的电路。编码数据在大多数输出设备中为用户界面进行解码,如监视器,计算器,打印机等。在信息由编码器编码之后一次。在本文中,我们将研究不同类型的二进制解码器。

二进制解码器

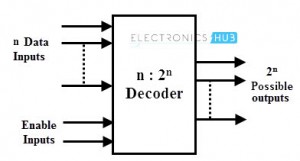

二进制解码器是一个多输入的多输出组合电路,它将N个输入线的二进制码转换为2N输出代码中的一个。当需要基于N位输入值时需要恰好激活2N输出中的一个时,使用这些。

下图显示了二进制解码器的一般结构,其中在N个输入线上接受编码信息,并且输出在2N可能的输出线中产生。

通常,解码器提供使能输入,以便根据数据输入激活已解码的输出。例如,对于BCD码,从0000到1001的4位组合足以表示十进制数字0到9。

根据输入行数的不同,二进制代码的输入可以是2位、3位或4位代码。当2n行可用时,它通过在接收n个输入时取消激活(使逻辑为0)所有其他输入来激活它的输出之一。

通常,输出代码中的位数大于其输入代码中的位。最常用的实用二进制解码器是2到4个解码器,3到8个解码器和4到16行二进制解码器。

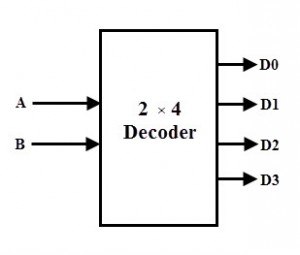

2到4二进制译码器

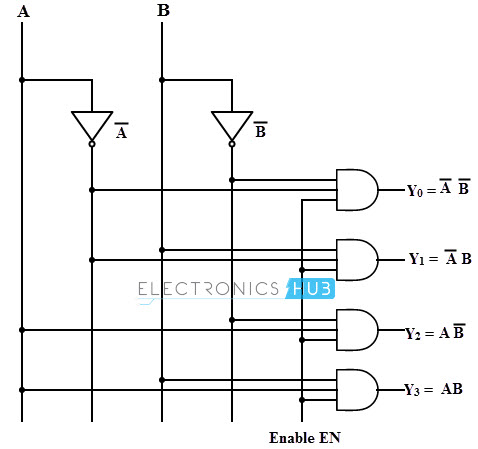

在2- 4二进制解码器中,两个输入被解码成四个输出,因此它由两个输入行和4个输出行组成。在任何时候,只有一个输出是有效的,而其他输出保持在逻辑0,并且保持有效或高的输出是由两个二进制输入A和B决定的。

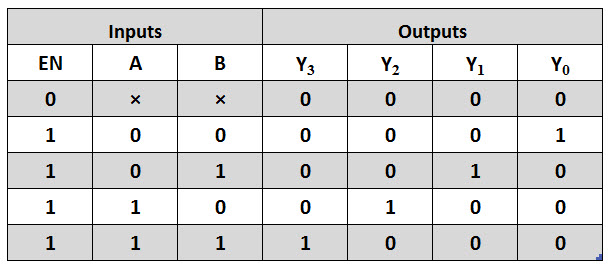

下图显示了2到4解码器的真值表。对于给定的输入,如果使能输入EN是高有效的(EN = 1),输出Y0到Y3是高有效的。当输入a和B都是低的(或a = B= 0),输出Y0是有效的或高,所有其他输出都是低的。

当A = 0和B = 1时,输出Y1将被激活,当A = 1和B = 0时,输出Y2将被激活。当两个输入都很高时,输出Y3也会很高。如果使能位为零,那么所有输出将被设置为零。输入和输出之间的关系在下面的真值表中清楚地说明。

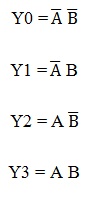

从上面的真值表中,我们可以获得每个输出的布尔表达式

这些表达式可以通过使用基本逻辑门来实现。因此,下面给出了2到4行译码器的逻辑电路设计,该译码器采用NOT和and门实现。两个非门或逆变器提供输入的补充。

通用使能线连接到每个和门,使得当EN = 0时,所有输出都是零,如果EN = 1,则取决于输入A和B,产生输出。每个输出代表2个输入变量的minterms之一。

还可以使用NAND门设计2-4解码器,如下图所示以及真相表。这是以最大术语的原则构建为输出。要生成minterms,我们必须使用充当逆变器的NAND门。如果两个输入为零(a = b = 0),则Y0将为零,如果a = 0和b = 1,则Y1将为1等。

因此,在给定的时间内,对于任何输入组合,只有一个输出是低的,所有其他输出都是高的。这种类型的解码器可在IC形式,使3至8,4至16,和5至32解码器还可以根据应用需求。

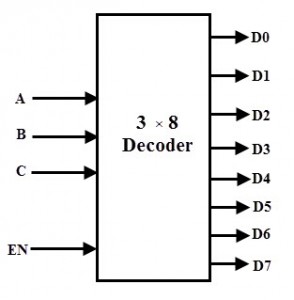

3-to-8译码器

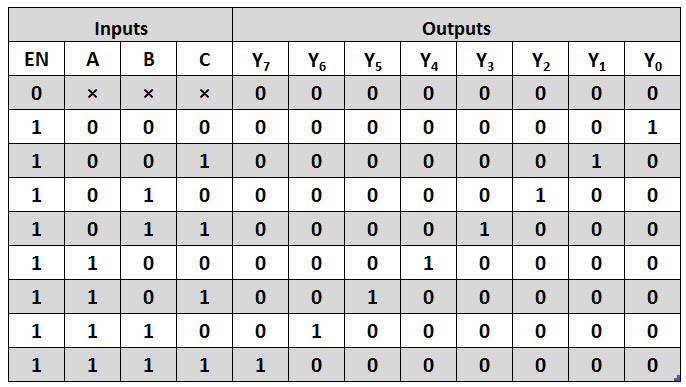

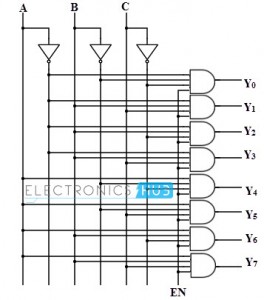

在3到8个解码器中,三个输入被解码为八个输出。它有三个输入作为A,B和C,以及来自Y0到Y7的八个输出。基于三个输入的组合,只选择了八个输出中的一个。

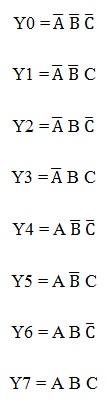

下图显示了3到8个解码器的真相表。提供启用输入以激活解码输出取决于输入组合A,B和C.假设A = B = 1和C = 0,则输出Y6为1,并且所有其他输出都为零。因此,从真相表中,Minterms表示每个输出方程,并且被给出

利用上述各输出项的最小项表达式,可以用3个NOT门和8个and门实现3- 8译码器电路。每个NOT门提供输入的补码,and门生成其中一个中项。

激活解码输出取决于输入数据。这个解码器的逻辑图如下所示。

对于一个特定的输入组合,8个输出中只有一个是高的,这就是为什么这个解码器也称为1- 8解码器。假设,当ABC = 011时,只有AND门4的所有输入都是高的,因此Y3是高的。

同样,在输入时的3位二进制数在输出时被转换为8位(相当于八进制),这就是方法;它也被称为二进制到八进制译码器

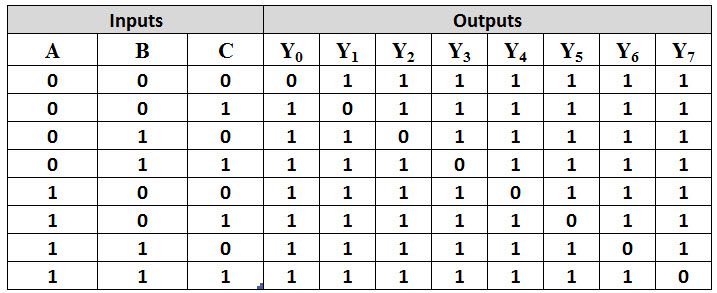

它也可以使用最大术语表示每个输出方程。在这种情况下,在逻辑电路中执行比电路的反演操作,分钟术语。下图显示了使用NAND门的3-8线解码器的真实表。表中的每个输出都具有最大术语表示。

在一个给定的时间,只有一个输出是低的,所有其他输出将是高的。例如,当A=B= 1, C=0时,输出Y6为零,其他输出均为高,如下图所示。

由上表可知,3到8行译码器采用3个非门和3个非门。如下图所示,非门产生输入的补码,而非门产生每个输出的最大项。

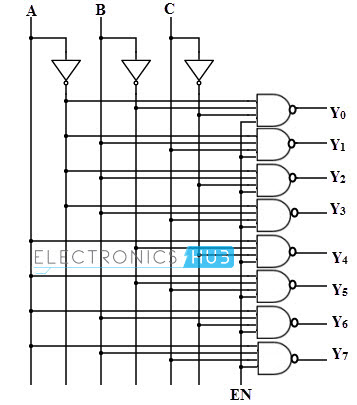

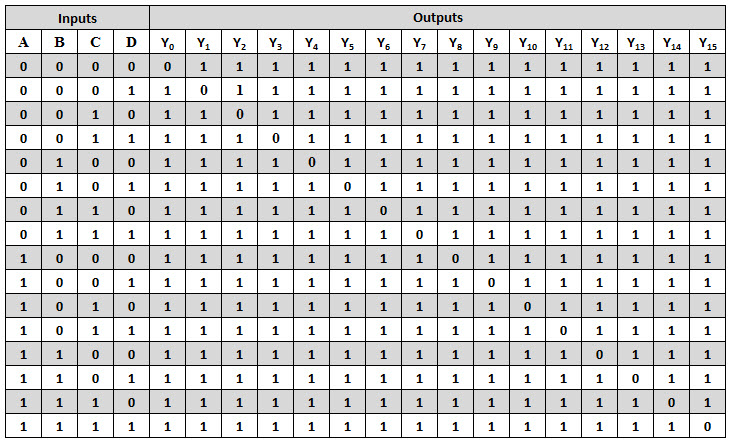

4至16个解码器

4比16解码器由4个输入和16个输出组成。类似于上面讨论的所有解码器,在这种情况下,在给定时间也只有一个输出将低,并且所有其他输出都很高(使用maxterms)。

这类解码器的真值表如下所示。如果这个解码器的输入是1000,那么输出Y8将是低的,所有其他输出将是高的,如图所示。这对于所有的输入组合都是如此。

从上述真理表中,可以通过使用4个不是栅极和16解码NAND门来实现4到16个解码器。为了解码4位输入的所有可能组合,需要16个(24 = 16)解码门。

值得注意的是,所有NAND门都在该电路上实现,产生如图所示的有效低输出。

由于它选择了基于特定输入组合的16个输出中的一个,因此这些解码器也称为16个解码器。其输出代表了十六位数作为十六进制数系,这种类型的解码器也称为二进制到十六进制解码器。

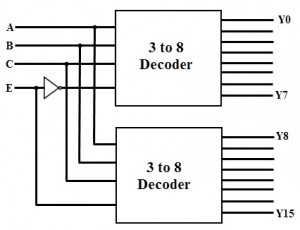

可以组合或级联两个或更多个解码器以产生具有较大数量的输入比特的解码器,利用解码器的启用输入。下面给出了两个3至8线解码器的级联组合。它由四个输入A,B,C并使E和16输出Y0至Y7组成。

其中一个输入变量用作启用第一3-4解码器的启用输入,并且该相同的输入互补并连接为启用第二解码器的输入。要启用的解码器由最重要的输入变量决定,其他输入变量被馈送到每个解码器。

当启用输入为零时,在禁用另一个时,将启用顶部解码器。然后,顶部解码器8输出生成Minterms 0000至0111.同样,当启用为1时,启用较低的解码器,并禁用顶部。因此,底部解码器输出从1000到1111生成minterms。

解码器的应用

解码器非常适用于仅在输入电平的特定组合的发生时激活特定输出或输出组的应用程序。通常,这些输入水平由寄存器或计数器的输出提供。

当计数器或寄存器连续脉冲解码器输入时,输出将按顺序被激活。这些输出可作为序列信号或定时信号,用于在特定时间切换设备。

二进制到十进制解码器

解码器用于获取对应于特定输入组合的十进制数字。BCD号码需要4个二进制数字来表示0到9位数,因此由4条输入线组成。它由10个输出线组成,对应于0到9位十进制数字。T.

这种类型的解码器也称为1到10解码器。对于特定输入组合,将激活输出对应于输入组合的十进制等效物。

地址解码器

在许多用途中,解码器广泛用于解码计算机存储器系统中的特定存储器位置。解码器接受CPU生成的地址代码,该地址代码是存储器中特定位置的地址位的组合。

在存储系统中,组合有几个存储器IC,每个存储器IC具有它们的唯一地址以区分其他存储器位置。

在这种情况下,在存储IC电路中内置的解码器被用来通过解码系统地址的最有效位来选择响应一系列地址的存储IC,从而选择特定的存储位置或IC。

在更复杂的存储系统中,存储ic或芯片被安排在多个银行中。当微处理器想要一次访问一个或多个字节时,必须同时或单独地选择这些行。

在这种情况下,必须激活多个解码器。为此,使用级联解码器或者最常用的解码器用可编程逻辑设备替换。

指令解码器

解码器的另一个应用可以在中央处理单元的控制单元中找到。该解码器用于解码程序指令,以便激活特定控制线,使得执行CPU的ALU中的不同操作。

4回复

谢谢!

我在Hutton32 JVN细胞自动机中设计一些电子产品。这篇文章完全解决了我的问题,如何从BIN>BCD转换器输出数据到7段。

这个网站非常熟练..

谢谢。

这确实是非常有用的网站!

这是学习数字电子产品的最佳网站